# This Page Is Inserted by IFW Operations and is not a part of the Official Record

# **BEST AVAILABLE IMAGES**

Defective images within this document are accurate representations of the original documents submitted by the applicant.

Defects in the images may include (but are not limited to):

- BLACK BORDERS

- TEXT CUT OFF AT TOP, BOTTOM OR SIDES

- FADED TEXT

- ILLEGIBLE TEXT

- SKEWED/SLANTED IMAGES

- COLORED PHOTOS

- BLACK OR VERY BLACK AND WHITE DARK PHOTOS

- GRAY SCALE DOCUMENTS

# IMAGES ARE BEST AVAILABLE COPY.

As rescanning documents will not correct images, please do not report the images to the Image Problem Mailbox.

Docket No.: 65933-071 PATENT

#### IN THE UNITED STATES PATENT AND TRADEMARK OFFICE

In re Application of : Customer Number: 20277

Ryosuke USUI : Confirmation Number:

Serial No.: : Group Art Unit:

Filed: February 24, 2004 : Examiner: Unknown

For: SEMICONDUCTOR DEVICE AND METHOD FOR MANUFACTURING SAME

# CLAIM OF PRIORITY AND TRANSMITTAL OF CERTIFIED PRIORITY DOCUMENT

Mail Stop CPD Commissioner for Patents P.O. Box 1450 Alexandria, VA 22313-1450

Sir:

In accordance with the provisions of 35 U.S.C. 119, Applicant hereby claims the priority of:

Japanese Patent Application No. 2003-068145, filed March 13, 2003

cited in the Declaration of the present application. A certified copy is submitted herewith.

Respectfully submitted,

MCDERMOTT, WILL & EMERY

Arthur J. Steiner W. Registration No. 26,106

600 13<sup>th</sup> Street, N.W. Washington, DC 20005-3096 (202) 756-8000 AJS:tlb Facsimile: (202) 756-8087

Date: February 24, 2004

65933-071 USUI € February 24,2004

# 日本国特許庁 JAPAN PATENT OFFICE

McDermott, Will & Emery

別紙添付の書類に記載されている事項は下記の出願書類に記載されている事項と同一であることを証明する。

This is to certify that the annexed is a true copy of the following application as filed with this Office.

出 願 年 月 日 Date of Application:

2003年 3月13日

出 願 番 号 Application Number:

特願2003-068145

[ST. 10/C]:

[JP2003-068145]

出 願 人

Applicant(s):

三洋電機株式会社

2004年 1月 9日

特許庁長官 Commissioner, Japan Patent Office 今井康

【書類名】

特許願

【整理番号】

NPC1030001

【提出日】

平成15年 3月13日

【あて先】

特許庁長官殿

【国際特許分類】

H01L 23/28

【発明者】

【住所又は居所】

大阪府守口市京阪本通2丁目5番5号 三洋電機株式会

社内

【氏名】

臼井 良輔

【特許出願人】

【識別番号】

000001889

【氏名又は名称】

三洋電機株式会社

【代理人】

【識別番号】

100105924

【弁理士】

【氏名又は名称】

森下 賢樹

【電話番号】

03-3461-3687

【手数料の表示】

【予納台帳番号】

091329

【納付金額】

21,000円

【提出物件の目録】

【物件名】

明細書 1

【物件名】

図面 1

【物件名】

要約書 1

【プルーフの要否】

要

#### 【書類名】 明細書

【発明の名称】 半導体モジュールおよびその製造方法

# 【特許請求の範囲】

【請求項1】 絶縁層と、

前記絶縁層内に埋設された配線と、

前記絶縁層上に搭載された回路素子と、

前記回路素子を覆うように形成された封止層と、

前記封止層を覆うように形成された導電性の遮蔽膜と、

## を含み、

前記配線と前記遮蔽膜とが電気的に接続していることを特徴とする半導体モジュール。

【請求項2】 請求項1に記載の半導体モジュールにおいて、

前記遮蔽膜を覆うように形成され、前記遮蔽膜を構成する材料よりも腐食耐性 の高い材料により構成された保護膜をさらに含むことを特徴とする半導体モジュ ール。

【請求項3】 絶縁層と、前記絶縁層内に埋設された配線と、前記絶縁層表面に搭載された回路素子と、前記回路素子を覆うように形成された封止層と、を含む積層体を分割して前記回路素子を含む半導体モジュールを製造する方法であって、

前記積層体の表面に分割溝を形成して前記配線の側面を露出させる工程と、前記積層体の表面側を導電性材料で覆い、前記配線と電気的に接続した遮蔽膜を形成する工程と、

前記積層体を裏面から前記分割溝に沿って切断し、当該積層体の前記回路素子を他の領域から分割する工程と、

を含むことを特徴とする半導体モジュールの製造方法。

【請求項4】 請求項3に記載の半導体モジュールの製造方法において、 前記配線を接地させる工程をさらに含むことを特徴とする半導体モジュールの 製造方法。

【請求項5】 請求項3または4に記載の半導体モジュールの製造方法にお

いて、

前記絶縁層上には複数の回路素子が搭載され、前記配線の側面を露出させる工程の前において、前記配線は前記複数の回路素子に接続して設けられ、

前記配線の側面を露出させる工程において、前記配線を分割し、当該分割された各配線が各前記回路素子にそれぞれ接続されるように前記分割溝を形成することを特徴とする半導体モジュールの製造方法。

【請求項6】 請求項3乃至5いずれかに記載の半導体モジュールの製造方法において、

前記遮蔽膜を、当該遮蔽膜を構成する材料よりも腐食耐性の高い材料により構成された保護膜で覆う工程をさらに含むことを特徴とする半導体モジュールの製造方法。

# 【発明の詳細な説明】

$[0\ 0\ 0\ 1]$

【発明の属する技術分野】

本発明は、回路素子を搭載した半導体モジュールおよびその製造方法に関する

[0002]

【従来の技術】

近年、携帯電話、PDA、DVC、DSCといったポータブルエレクトロニクス機器の高機能化が加速している。これに伴い、これらのエレクトロニクス機器に使用されるLSIに対しても高機能化、高性能化が要求されている。このため、LSIの動作クロックも高周波となっている。また、このようなエレクトロニクス機器が市場で受け入れられるためには、小型・軽量化が必須となっており、それを実現するために高集積のLSIが求められている。

[0003]

このように、高周波のLSIを小型に実装するため、半導体チップ間の距離が 短くなり高密度となり、ノイズの影響が大きくなるという問題がある。従来、ノイズ対策として、半導体装置のパッケージを金属の封止材で覆う技術が開示されている(たとえば特許文献 1)。

# [0004]

ところで、従来、高周波用LSIを小型でパッケージ化する技術として、CSPが知られている(たとえば特許文献 2)。同公報記載には、高周波用LSIを搭載するシステム・イン・パッケージが開示されている。このパッケージは、ベース基板上に、多層配線構造が形成され、その上に高周波用LSIをはじめとする回路素子が形成されている。多層配線構造は、コア基板や樹脂付銅箔などが積層された構造となっている。

## [0005]

しかしながら、これら従来のCSPでは、ポータブルエレクトロニクス機器等において現在望まれているような水準の小型化、薄型化、軽量化を実現することは難しかった。これは、従来のCSPはチップを支持する基板を有することによる。支持基板の存在により、パッケージ全体が厚くなり、小型化、薄型化、軽量化に限界があった。また、放熱性の改善にも一定の限界があった。

#### [0006]

こうした事情に鑑み、本出願人は、ISB(Integrated System in Board;登録商標)とよばれる新規なパッケージを開発した。 ISBとは、半導体ベアチップを中心とする電子回路のパッケージングにおいて、銅による配線パターンを持ちながら回路部品を支持するためのコア(基材)を使用しない独自のコアレスシステム・イン・パッケージである。特許文献3には、こうしたシステム・イン・パッケージが記載されている。

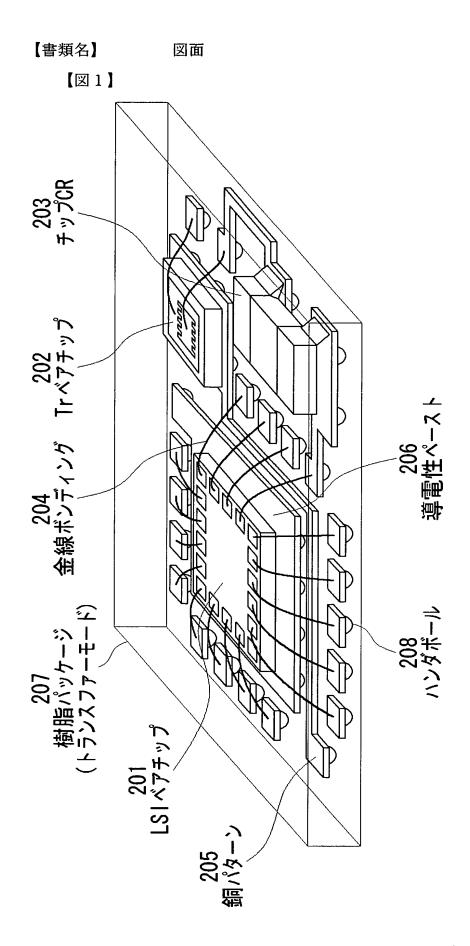

# [0007]

図1はISBの一例を示す概略構成図である。ここではISBの全体構造をわかりやすくするため、単一の配線層のみ示しているが、実際には、複数の配線層が積層した構造となっている。このISBでは、LSIベアチップ201、Trベアチップ202およびチップCR203が銅パターン205からなる配線により結線された構造となっている。LSIベアチップ201は、引き出し電極や配線と金線ボンディング204を介して導通されている。LSIベアチップ201の直下には、導電性ペースト206が設けられ、これを介してISBがプリント配線基板に実装される。ISB全体はエポキシ樹脂などからなる樹脂パッケージ

207により封止された構造となっている。

[0008]

このパッケージによれば、以下の利点が得られる。

- (i) コアレスで実装できるため、トランジスタ、IC、LSIの小型・薄型化を実現できる。

- (ii) トランジスタからシステムLSI、さらにチップタイプのコンデンサや抵抗を回路形成し、パッケージングすることができるため、高度なSIP(Sys tem in Package)を実現できる。

- (iii) 現有の半導体チップを組み合わせできるため、システムLSIを短期間に開発できる。

- (iv) 半導体ベアチップが直下の銅材に直接マウントされており、良好な放熱性を得ることができる。

- (v)回路配線が銅材でありコア材がないため、低誘電率の回路配線となり、高速データ転送や高周波回路で優れた特性を発揮する。

- (vi) 電極がパッケージの内部に埋め込まれる構造のため、電極材料のパーティクルコンタミの発生を抑制できる。

- (vii)パッケージサイズはフリーであり、1 個あたりの廃材を64 ピンのSQ F P パッケージと比較すると、約1/10 の量となるため、環境負荷を低減できる。

- (viii) 部品を載せるプリント回路基板から、機能の入った回路基板へと、新しい概念のシステム構成を実現できる。

- (ix) ISBのパターン設計は、プリント回路基板のパターン設計と同じように容易であり、セットメーカーのエンジニアが自ら設計できる。

[0009]

【特許文献1】

特開平5-47962号公報

【特許文献2】

特開2002-94247号公報

【特許文献3】

特開2002-110717号公報

# [0010]

# 【発明が解決しようとする課題】

上述した特許文献1で開示された、半導体装置のパッケージを金属の封止材で 覆う技術では、半導体装置とは別部品として、プリント基板に封止材を実装して いるため、封止材形成後のパッケージのサイズが大きくなり小型化が図れないと 問題があった。また、封止材を半導体装置と別部品として形成するため、生産性 が低いという問題もあった。

## $[0\ 0\ 1\ 1]$

本発明は、上記事情に鑑みなされたものであり、その目的は、簡易な方法で半導体モジュールのノイズ対策を行う技術を提供することにある。本発明の別の目的は、半導体モジュールを小型・軽量化する技術を提供することにある。本発明のまた別の目的は、半導体モジュールの生産性を向上する技術を提供することにある。

#### $[0\ 0\ 1\ 2]$

# 【課題を解決するための手段】

本発明によれば、絶縁層と、絶縁層内に埋設された配線と、絶縁層上に搭載された回路素子と、回路素子を覆うように形成された封止層と、封止層を覆うように形成された導電性の遮蔽膜と、を含み、配線と遮蔽膜とが電気的に接続していることを特徴とする半導体モジュールが提供される。ここで、遮蔽膜は電磁波を遮蔽する機能を有する。これにより、ノイズの影響を低減することができる。遮蔽膜に電気的に接続された配線は接地することができる。これにより、遮蔽膜をも接地することができ、電磁波を遮蔽することができる。

#### [0013]

遮蔽膜は、配線と同じ材料により構成することができる。遮蔽膜は、たとえば 銅を主成分として構成することができる。また、配線は、回路素子にも電気的に 接続して構成することができる。半導体モジュールをISBで構成した場合、回 路素子に電気的に接続された配線のいずれかは接地される。本発明の半導体モジ ュールにおいて、遮蔽膜が、このように接地される配線と電気的に接続されるよ うに構成することができる。

# [0014]

本発明の半導体モジュールは、遮蔽膜を覆うように形成され、遮蔽膜を構成する材料よりも腐食耐性の高い材料により構成された保護膜をさらに含むことができる。保護膜は、たとえばニッケルや金等により構成することができる。

# [0015]

このようにすれば、遮蔽膜により半導体モジュールを遮蔽することができると ともに、遮蔽膜表面を腐食耐性の高い保護膜により保護することができるので、 遮蔽膜の機能を長期間維持することができる。

#### $[0\ 0\ 1\ 6\ ]$

本発明によれば、絶縁層と、絶縁層内に埋設された配線と、絶縁層表面に搭載され、配線に電気的に接続された回路素子と、回路路素子を覆うように形成された封止層と、を含む積層体を分割して回路素子を含む半導体モジュールを製造する方法が提供される。この半導体モジュールの製造方法は、上記積層体の表面に分割溝を形成して配線の側面を露出させる工程と、積層体の表面側を導電性材料で覆い、配線と電気的に接続した遮蔽膜を形成する工程と、積層体を裏面から分割溝に沿って切断し、当該積層体の回路素子を他の領域から分割する工程と、を含む。

# $[0\ 0\ 1\ 7]$

このようにすれば、回路素子を他の領域から分割する工程と組み合わせて遮蔽膜を形成することができるので、簡易な方法で半導体モジュールのノイズ対策を行うことができる。これにより、半導体モジュールの生産性を向上することができる。

#### [0018]

本発明の半導体モジュールの製造方法において、配線を接地させる工程をさらに含むことができる。配線は、回路素子にも電気的に接続して構成することができる。

#### [0019]

本発明の半導体モジュールの製造方法において、絶縁層上には複数の回路素子

が搭載されてよく、配線の側面を露出させる工程の前において、配線は複数の回路素子に接続して設けられてよく、配線の側面を露出させる工程において、配線を分割し、当該分割された各配線が各回路素子にそれぞれ接続されるように分割溝を形成することができる。

#### [0020]

本発明の半導体モジュールの製造方法において、導電性材料は銅を主成分とすることができる。

### [0021]

本発明の半導体モジュールの製造方法において、めっき法により遮蔽膜を形成することができる。また、遮蔽膜は、スクリーン印刷法を用いて導電性ペーストを付着させることにより形成することもできる。

#### [0022]

本発明の半導体モジュールの製造方法において、遮蔽膜を、当該遮蔽膜を構成 する材料よりも腐食耐性の高い材料により構成された保護膜で覆う工程をさらに 含むことができる。

#### [0023]

#### 【発明の実施の形態】

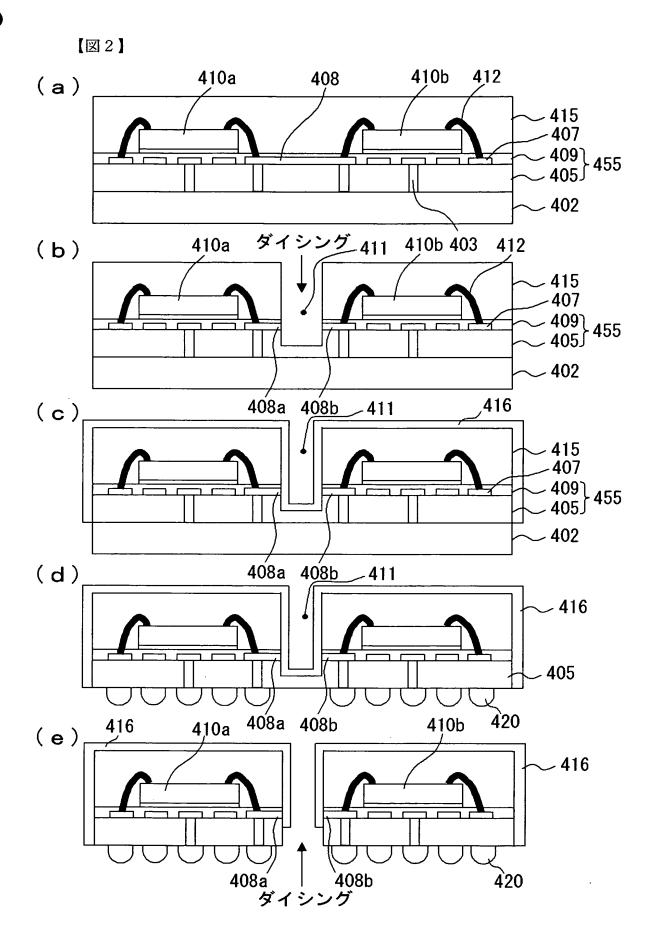

図2は、本発明の実施の形態における半導体モジュールの製造方法を示す工程 断面図である。

# [0024]

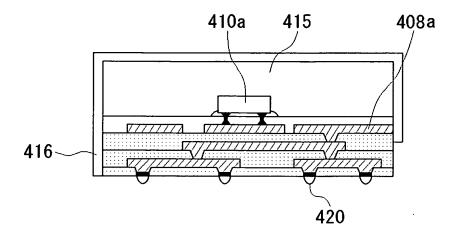

図2(a)は、半導体モジュールの製造途中における積層体を示す。ここで、 積層体は、金属箔402と、その上に形成された多層配線構造455と、その上 に形成された第一の回路素子410aおよび第二の回路素子410bと、回路素 子410aおよび回路素子410bを覆うように形成された封止膜415とを含 む。多層配線構造455は、層間絶縁膜405と、層間絶縁膜405に設けられ たビア403と、ビア403に電気的に接続された配線407および被切断配線 408と、配線407および被切断配線408を覆うように形成された絶縁膜4 09とを有する。ここでは、多層配線構造455を省略して記載しているが、多 層配線構造455は、複数のビア、配線、および絶縁膜が積層した構造を有する [0025]

0

第一の回路素子410aおよび第二の回路素子410bは、たとえば、トランジスタ、ダイオード、ICチップ等の半導体素子、チップコンデンサ、チップ抵抗等の受動素子である。第一の回路素子410aおよび第二の回路素子410bは、ワイヤ412により配線407および被切断配線408に適宜電気的に接続される。ここで、被切断配線408は、第一の回路素子410aおよび第二の回路素子410bに共通に接続されている。多層配線構造455の詳細な構造およびこの段階までの積層体の製造方法については後述する。

[0026]

以下、このように構成された積層体を分割して半導体モジュールを製造する工程を説明する。

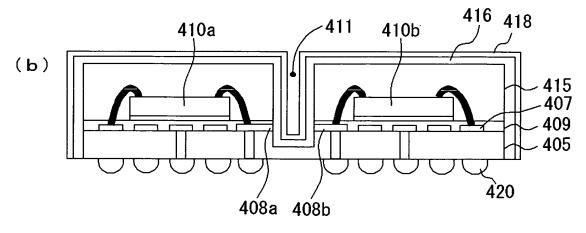

まず、積層体を、表面側(図中上側)から層間絶縁膜405の途中までダイシングして分割溝411を形成する(図2(b))。これにより、被切断配線408は第一の回路素子410aに接続した配線408aと第二の回路素子410bに接続した配線408bとに分割され、配線408aおよび配線408bともに分割溝411の側面に露出する。

#### [0027]

つづいて、半導体モジュールの表面を覆うように遮蔽膜416を形成する(図2(c))。遮蔽膜416は、配線407および被切断配線408を構成する金属と同じ材料により構成することができる。遮蔽膜416は、たとえば銅や銀等の比較的低抵抗な金属により構成される。また、遮蔽膜416は、半導体モジュールを構成する他の構成要素、たとえば封止膜415、配線407、層間絶縁膜405、絶縁膜409等と線膨張係数の差が少ない材料により構成されるのが好ましい。遮蔽膜416は、たとえばめっき法、スパッタリング法、CVD法等で形成することができる。めっき法で遮蔽膜416を形成する場合、たとえば硫酸銅等の化学銅を用いて無電解めっきを行い半導体モジュールの表面に銅の薄膜を形成した後、電解めっきする。電解めっきは、たとえば半導体モジュールの表面側を液温約25℃の硫酸銅水溶液に浸漬して行うことができる。遮蔽膜416は

、配線408aおよび配線408bと電気的に接続するように形成される。遮蔽膜416は、半導体モジュール全体を覆うように形成した後、裏面側をパターニングして不要な遮蔽膜416を除去して形成することもでき、また半導体モジュールの表面側のみをめっき液に浸漬して形成することもできる。また、遮蔽膜416は、スクリーン印刷法を用いて導電性ペーストを付着させることにより形成することもできる。

# [0028]

その後、金属箔402を除去する。金属箔402の除去は、研磨、研削、エッチング、レーザの金属蒸発等により行うことができる。つづいて露出したビア403に半田等の導電材を被着して多層配線構造455の裏面に半田ボール420を形成する(図2(d))。配線408aおよび配線408bに接続された半田ボール420は接地される。これにより、遮蔽膜416をも接地することができ、半導体モジュールのノイズを遮断する機能を担保することができる。

# [0029]

つづいて、分割溝411に沿って、半導体モジュールの裏面側から再びダイシングして半導体モジュールを分割する(図2 (e))。ここで、裏面側からのダイシングは、各半導体モジュールにおいて、遮蔽膜416がそれぞれ配線408 a および配線408 b と接続した状態を保つように行う。これにより半導体モジュールが完成する。

#### [0030]

本実施の形態において、図2 (d)に示した金属箔402の除去工程を行うまでは、金属箔402が支持基板となる。金属箔402は、ビア403、配線407、および被切断配線408形成時や遮蔽膜416形成時の電解めっき工程において電極としても利用される。また、封止膜415をモールドする際にも、金型への搬送、金型への実装の作業性を良好にすることができる。

#### [0031]

以上のように、本発明によれば、半導体モジュールの製造途中で、簡易な方法 で半導体モジュール表面に遮蔽膜 4 1 6 を形成することができ、ノイズ対策を行 うことができる。これにより、半導体モジュールの生産性を向上することもでき る。また、本発明によれば、回路素子がモールドされている封止膜415表面に 直接遮蔽膜416が形成されるので、半導体モジュールを小型・軽量化すること ができる。

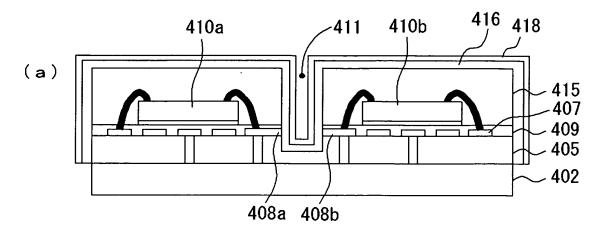

# [0032]

遮蔽膜416は、図3に示すように、保護膜418で覆われた構成とすることもできる。図2(c)を参照して説明したのと同様に遮蔽膜416を形成した後、遮蔽膜416上にたとえばめっき法、スパッタリング法、CVD法により保護膜418を形成する(図3(a))。保護膜418は、遮蔽膜416を構成する金属よりも腐食耐性の高い材料により構成される。このような材料として、たとえばニッケルや金等が例示される。つづいて、金属箔402を除去して半田ボール420を形成する(図3(b))。その後、半導体モジュールの裏面側からダイシングして半導体モジュールを分割する(図3(c))。

#### [0033]

このようにすれば、遮蔽膜416により半導体モジュールの第一の回路素子410aおよび第二の回路素子410bを遮蔽することができるとともに、遮蔽膜416表面を腐食耐性の高い保護膜418により保護することができるので、遮蔽膜416の機能を長期間維持することができる。

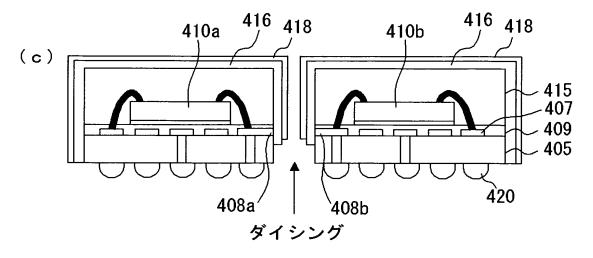

# [0034]

図4は、図2に示した多層配線構造455部分を詳細に示す半導体モジュールの断面図である。図2では、多層配線構造455を省略して記載したが、多層配線構造455は、層間絶縁膜405および配線407からなる配線層が複数層積層した多層配線構造体より構成されている。

#### $[0\ 0\ 3\ 5]$

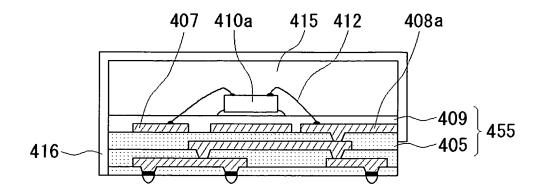

以下、図5および図2 (a)を参照して、図2 (a)に示した段階までの積層体の製造方法を説明する。

まず、金属箔402表面上の所定の領域に選択的に導電被膜422を形成する (図5(a))。具体的には、フォトレジスト(不図示)で金属箔402を被覆 した後、所定の領域のフォトレジストを除去して金属箔402表面の一部を露出 させる、つづいて、電解めっき法により、金属箔402の露出面に導電被膜42 2 を形成する。導電被膜 4 2 2 の膜厚は、例えば  $1\sim10$   $\mu$  m程度とする。この 導電被膜 4 2 2 は、最終的に半導体モジュールの裏面電極となるので、半田等の ロウ材との接着性の良い金、または銀を用いて形成することが好ましい。 金属 箱 4 0 2 の主材料は、C u 、A 1 、F e -N i 等の合金等とすることが好ましい。 ロウ材の付着性やめっき性が良好だからである。金属箱 4 0 2 の厚さは、特に 制限はないが、たとえば 1 0  $\mu$  m  $\sim$  3 0 0  $\mu$  m程度とすることができる。

# [0036]

導電被膜422の形成に用いたレジストを除去した後、金属箔402上に、第一層目の配線パターンを形成する。まず金属箔402を化学研磨して表面のクリーニングと表面粗化を行う。次に、金属箔402上に熱硬化性樹脂を堆積して導電被膜422全面を覆い、加熱硬化させて平坦な表面を有する層間絶縁膜405を形成する。層間絶縁膜405を構成する樹脂材料としては、BTレジン等のメラミン誘導体、液晶ポリマー、エポキシ樹脂、PPE樹脂、ポリイミド樹脂、フッ素樹脂、フェノール樹脂、ポリアミドビスマレイミド等の熱硬化性樹脂が例示される。このうち、高周波特性に優れる液晶ポリマー、エポキシ樹脂、BTレジン等のメラミン誘導体が好適に用いられる。これらの樹脂とともに、適宜、フィラーや添加剤を添加してもよい。

# [0037]

つづいて、層間絶縁膜405中にたとえば炭酸ガスレーザー、機械加工、薬液による化学エッチング加工、プラズマを用いたドライエッチング法等によりビアホール424を形成する。その後、エキシマレーザーを照射してエッチング滓を除去し、つづいて、ビアホール424を埋め込むように全面に銅めっき層を形成する。この銅めっき層はビアホール424の段差で断線しないように、まず無電解銅めっきにより全面に $0.5\mu$ m程度の薄膜を形成した後、電解めっきにより約 $20\mu$ m程度の厚みに形成する。無電解めっき用触媒は、通常パラジウムを用いることが多く、可とう性の絶縁基材に無電解用めっき用触媒を付着させるには、パラジウムを錯体の状態で水溶液に含ませ、可とう性の絶縁基材を浸漬して表面にパラジウム錯体を付着させ、そのまま、還元剤を用いて、金属パラジウムに還元することによって可とう性の絶縁基材表面にめっきを開始するための核を形

成することができる。通常は、このような操作をするために、被めっき物を、アルコールや酸で洗浄し、表面に付着した油分を除去しておく。

# [0038]

その後、フォトレジストをマスクとして銅めっき層をエッチングし、銅からなる配線407を形成する(図5(b))。このとき、ビア403も形成される。配線407は、たとえば、レジストから露出した箇所に、化学エッチング液をスプレー噴霧して不要な銅箔をエッチング除去することにより形成することができる。エッチングレジストは、通常のプリント配線板に用いることのできるエッチングレジスト材料を用いることができ、レジストインクをシルクスクリーン印刷して形成したり、エッチングレジスト用感光性ドライフィルムを銅箔の上にラミネートして、その上に配線導体の形状に光を透過するフォトマスクを重ね、紫外線を露光し、露光しなかった箇所を現像液で除去して形成することができる。化学エッチング液には、塩化第二銅と塩酸の溶液、塩化第二鉄溶液、硫酸と過酸化水素の溶液、過硫酸アンモニウム溶液など、通常のプリント配線板に用いる化学エッチング液を用いることができる。

#### [0039]

その後、配線 4 0 7 を覆うようにしてさらに層間絶縁膜 4 0 5 を形成した後、同様の手順を繰り返すことにより、ビアホール 4 2 4 、ビア 4 0 3 、配線 4 0 7 、および被切断配線 4 0 8 の積層構造を形成する(図 5 (c))。

#### [0040]

図2(a)に戻り、多層配線構造455の最上層には、絶縁膜409を形成する。絶縁膜409を構成する材料としては、たとえばエポキシ樹脂、アクリル樹脂、ウレタン樹脂、ポリイミド樹脂等の樹脂、および、これらの混合物、さらに、これらの樹脂にカーボンブラック、アルミナ、窒化アルミニウム、窒化ホウ素、酸化スズ、酸化鉄、酸化銅、タルク、雲母、カオリナイト、炭酸カルシウム、シリカ、酸化チタン等の無機フィラーを混合したもの等が例示される。

#### $[0\ 0\ 4\ 1]$

その後、絶縁膜409の表面に第一の回路素子410aおよび第二の回路素子410bを搭載し、第一の回路素子410aおよび第二の回路素子410bをワ

イヤ412を介して配線407および被切断配線408と接続する。第一の回路素子410aおよび第二の回路素子410bは、たとえば半田等のロウ材や接着剤等により絶縁膜409上に固着される。

# [0042]

次いで、これらの第一の回路素子410aおよび第二の回路素子410bを封止膜415でモールドする。第一の回路素子410aおよび第二の回路素子41 0bのモールドは、金型を用いて同時に行う。ここでは二つの回路素子しか示していないが、より多くの回路素子に対して同時にモールドをすることができる。封止膜415の形成は、トランスファーモールド、インジェクションモールド、ポッティングまたはディッピングにより実現できる。樹脂材料としては、エポキシ樹脂等の熱硬化性樹脂がトランスファーモールドまたはポッティングで実現でき、ポリイミド樹脂、ポリフェニレンサルファイド等の熱可塑性樹脂はインジェクションモールドで実現できる。

#### [0043]

また、以上の図2~図5では、回路素子410a(および回路素子410b)と配線407および配線408a(および配線408b)とをワイヤボンディング方式で接続する形態を示したが、図6に示すように回路素子410aをフェイスダウンに配置したフリップ実装とすることもできる。

#### $[0\ 0\ 4\ 4\ ]$

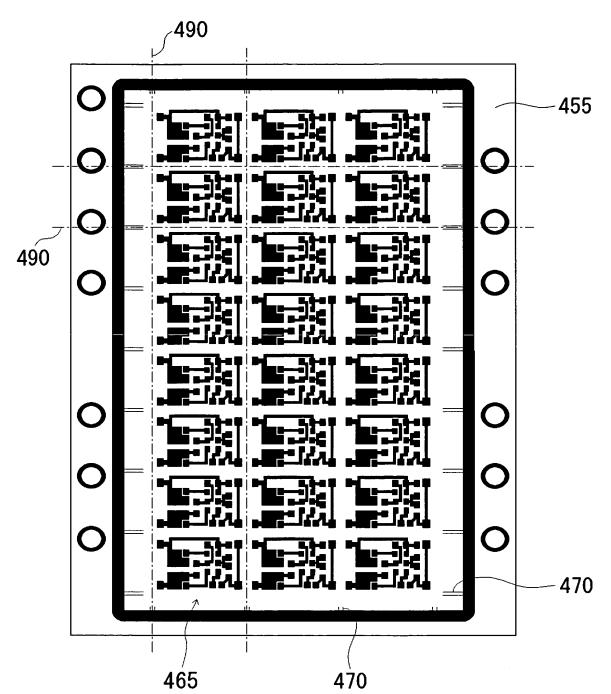

図7は、多層配線構造455上に形成された複数の半導体モジュール465がマトリクス状に形成された状態を示す図である。本実施の形態において、複数のモジュール上には封止膜415および遮蔽膜416が形成されているが、ここでは記載を省略している。複数のモジュール465は、ダイシングライン490に沿って分割される。本実施の形態において、金属箔を除去した後にダイシングするため、切断面の荒れやブレードの消耗を抑制することができる。また、多層配線構造455の表面に位置合わせマーク470を設けることにより、ダイシングラインの位置を迅速かつ正確に把握することができる。本実施の形態において、位置合わせマーク470は、多層配線構造455の表面から裏面にかけてホール状に形成されることが好ましい。これにより、裏面からダイシングを行う際にも

ダイシングラインの位置を正確に把握することができる。

# [0045]

なお、BGA等の従来のCSPにおいては、基板上に形成されたモジュールを 金型で打ち抜く方法が採用されている。そのため、本実施の形態で説明したよう にダイシング工程との組合せで遮蔽膜416を形成するような製造プロセスを従 来のCSPに適用するのは困難である。このように、本実施の形態で説明したよ うなISBを用いることにより、ダイシングで半導体モジュールを分割するとと もに遮蔽膜416をも形成することができ、製造プロセス上、大きなメリットが ある。

# [0046]

#### 【発明の効果】

以上説明したように本発明によれば、簡易な方法で半導体モジュールのノイズ 対策を行うことができる。本発明によれば、半導体モジュールを小型・軽量化す ることができる。さらに、本発明によれば、半導体モジュールの生産性を向上す ることができる。

#### 【図面の簡単な説明】

- 【図1】 ISBの一例を示す概略構成図である。

- 【図2】 本発明の実施の形態における半導体モジュールの製造方法を示す 工程断面図である。

- 【図3】 図2に示した半導体モジュールの変形例の製造方法を示す工程断面図である。

- 【図4】 図2に示した多層配線構造部分を詳細に示す半導体モジュールの 断面図である。

- 【図5】 図2に示した半導体モジュールの製造途中の積層体の製造方法を示す図である。

- 【図6】 回路素子をフェイスダウンに配置したフリップ実装とした半導体 モジュールの断面図である。

- 【図7】 多層配線構造上に複数の半導体モジュールがマトリクス状に形成された状態を示す図である。

# 【符号の説明】

201 LSIベアチップ、 202 Trベアチップ、 203 チップCR、 204 金線ボンディング、 205 銅パターン、 206 導電性ペースト、 207 樹脂パッケージ、 402 金属箔、 403 ビア、 405 層間絶縁膜、 407 配線、 408 被切断配線、 408a 配線、 408b 配線、 409 絶縁膜、 410a 第一の回路素子、 410b 第二の回路素子、 411 分割溝、 412 ワイヤ、 415 封止膜、 416 遮蔽膜、 418 保護膜、 420 半田ボール、 422 導電被膜、 424 ビアホール、 455 多層配線構造、 465 半導体モジュール、 470 マーク、 490 ダイシングライン。

【図3】

【図4】

【図6】

【書類名】 要約書

【要約】

【課題】 簡易な方法で半導体モジュールのノイズ対策を行う。

【解決手段】 半導体モジュールは、層間絶縁膜405および絶縁膜409と、 絶縁膜409内に埋設された配線407、408aおよび408bと、絶縁膜4 09上に搭載された回路素子410aおよび410bと、回路素子410aおよ び410bを覆うように形成された封止膜415と、封止膜415を覆うように 形成された導電性の遮蔽膜416と、を含む。配線408aおよび408bは、 遮蔽膜416に電気的に接続して構成される。

【選択図】 図2

# 出願人履歴情報

識別番号

[000001889]

1. 変更年月日 [変更理由] 1993年10月20日

住 所

住所変更

大阪府守口市京阪本通2丁目5番5号

氏 名 三洋電機株式会社